#### Application Note:

#### The Am79C30A Digital Subscriber Controller (DSC) and ISDN Layer I Impedance and Pulse Shape Recommendations

#### SCOPE:

This document is a technical application note to circuit board designers and transformer manufacturers interested in the interaction of the Am79C30A Digital Subscriber Controller (DSC) and the passive components of the ISDN S/T interface affecting impedance and pulse shape.

AMD ISDN Strategic Development June 28, 1991

# **Table of Contents**

| 1 | Connecting the DSC to the S/T Interface                                                                                                                                                    | 1                    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2 | Review of ISDN Electrical Requirements  2.1 Wiring Configuration and Line Termination  2.2 Impedance Template  2.3 Pulse Shape Templates  2.4 Balance Requirements  2.5 Other Requirements | 2<br>2<br>3<br>5     |

| 3 | Transformer Model                                                                                                                                                                          | 6                    |

| 4 | Parameter and Template Measurement                                                                                                                                                         | 9                    |

| 5 | Impedance Template                                                                                                                                                                         | 11                   |

| 6 | 50 Ohm Pulse Shape Template 6.1 Leading Edge Response 6.2 Pulse Amplitude 6.3 Trailing Edge Response                                                                                       | 13<br>14             |

| 7 | 400 Ohm Pulse Shape Template 7.1 Leading Edge Response 7.2 Pulse Amplitude 7.3 Trailing Edge Response 7.3.1 Leakage Inductance Component 7.3.2 Magnetizing Inductance Component            | 15<br>17<br>17<br>19 |

| 8 | 5.6 Ohm Pulse Requirements                                                                                                                                                                 | 20                   |

| 9 | Conclusion                                                                                                                                                                                 | 21                   |

| 1 | 0 Transformer Recommendations                                                                                                                                                              | 22                   |

# 1 Connecting the DSC to the S/T Interface

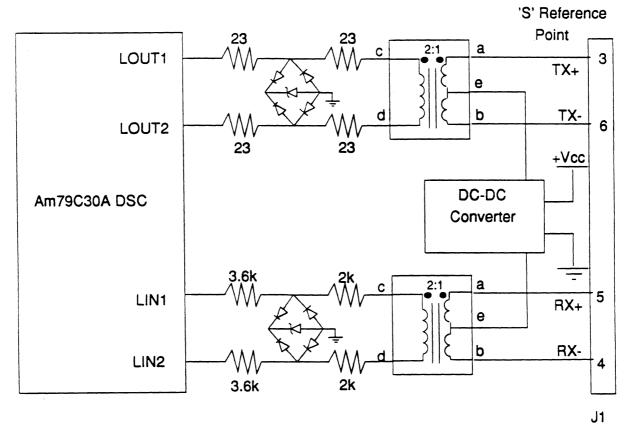

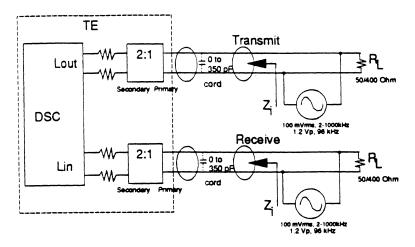

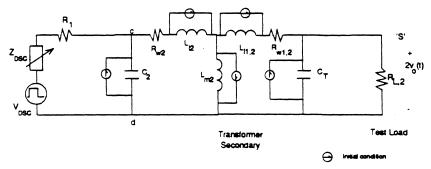

Figure 1.1 shows a typical application in which the DSC connects to the ISDN S or T reference point through current limiting resistors, a surge protection network, and an isolation transformer. Careful surge protection design and component selection is required to maintain S/T interface pulse shape and impedance requirements. Please see AMD's surge protection note for details on overvoltage protection.

In phantom feed applications, the transmit wire pair is typically biased to 48 VDC with respect to the receive wire pair by a DC power feed. The potential difference at the center-taps of the primary (line) sides of the two transformers is used to power the TE.

Series scaling and surge protection resistors on the transmitter are set to 92 Ohms total in this example. Actual values may vary slightly depending on transformer DC resistance.

Figure 1.1

Typical Connection of the DSC to the S Interface

## 2 Review of ISDN Electrical Requirements

Standards such as NET3 in Europe and ANSI T1.605 in North America have emerged to enable ISDN manufacturers to produce compatible products. Although variations occur from nation to nation, electrical requirements worldwide are based on the International Telegraph and Telephone Consultative Committee (CCITT) recommendation I.430.

#### 2.1 Wiring Configuration and Line Termination

The S or T reference points can be configured for point-to-point (one network termination, NT, and one terminal equipment, TE) or point-to-multipoint (one NT and several TE's) operation. The line is terminated at the NT with 100 Ohms and at the TE farthest from the NT with another 100 Ohms.

The recommendations apply to the terminal together with its associated access cord. Although the access cord provided may be less than 5 meters long, the TE with a detachable cord must support a cord of minimum length 5 meters. If a cord is not provided, the TE must meet electrical specifications with a standard ISDN basic access TE cord, which is described in §8.9 of I.430.

## 2.2 Impedance Template

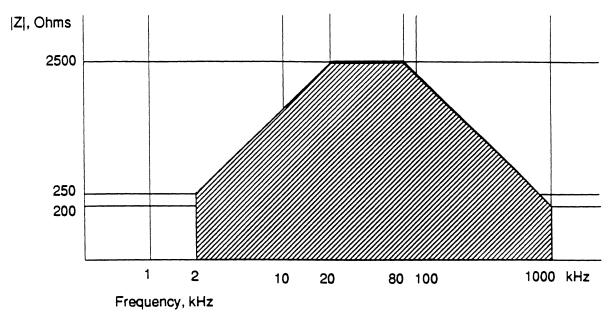

The first requirement is a template of minimum input impedance, using a test waveform of 100 mV rms minimum. It is applicable to the TE receiver at all times and to the TE transmitter during the pseudo-ternary space (binary 1) and during power down or deactivation. Figure 12/I.430 is repeated in Figure 2.2 for reference in the following discussion.

During a pseudo-ternary mark, the transmitter impedance must be at least 20 Ohms.

Figure 2.2 (Figure 12/I.430)

TE Impedance Template (log-log scale)

#### 2.3 Pulse Shape Templates

I.430 and T1.605 describe three pulse shape templates. The 50 Ohm test load represents the normal termination when one TE drives the line. The 400 Ohm test load represents eight TE's simultaneously driving a pulse of the same polarity. The 5.6 Ohm test load represents the condition in which two TE's simultaneously drive pulses of opposite polarity.

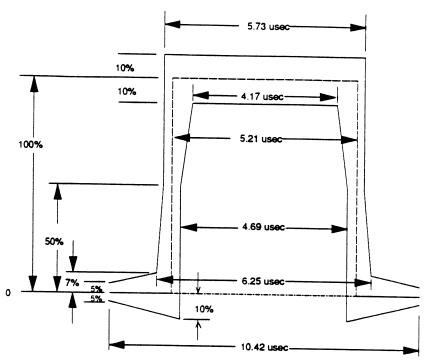

Figure 2.3.1 is reproduced from Figure 13/I.430 and is applicable to a transmitted pulse of positive or negative polarity when terminated with a 50 Ohm test

load. 100% corresponds to the nominal pulse amplitude of 750 mV.

Figure 2.3.1 Transmitter Output Pulse Template, 50 Ohm Load

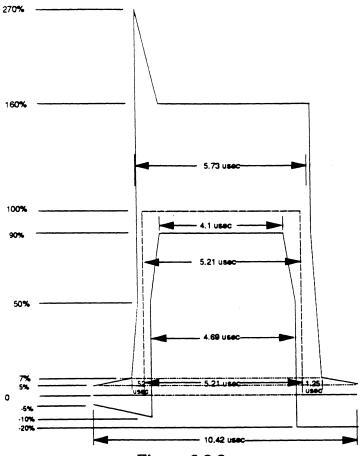

Figure 2.3.2 is reproduced from Figure 14/I.430 and is applicable to a isolated transmitted pulse of positive or negative polarity when terminated with a 400 Ohm test load. Framing pulses are followed by balancing bits and therefore do not meet the isolation criterion.

Figure 2.3.2 Template for an Isolated Pulse with a Test Load of 400 Ohms

Under the 5.6 Ohm test load condition, the pulse amplitude is limited to a maximum of 20% of the nominal amplitude, or 150 mV.

# 2.4 Balance Requirements

The transmitter and receiver must meet the following longitudinal conversion loss requirements, measured according to §4.1.3 of CCITT G.117. The balance requirements are influenced most directly by the transformer primary-side center-tap and the distribution of parasitic elements within the transformer.

LCL  $\geq$  54 dB 10 kHz  $\leq$  f  $\leq$  300 kHz with an allowable 20 dB/decade roll-off from 300 kHz to 1 MHz.

The transmitter must meet the following output signal balance requirements, measured according to §4.3.1 of CCITT G.117:

Ouput signal balance  $\geq 54$  dB 10 kHz  $\leq f \leq 96$  kHz with an allowable 20 dB/decade roll-off from 96 kHz to 1 MHz.

#### 2.5 Other Requirements

Power surge protection must also be considered when designing the connecting circuitry between the S/T reference point and the DSC. Often a surge protection device appears as a capacitive load across the interface terminal and therefore affects the pulse shape and impedance of the terminal. T1.605 §9.8 provides a baseline recommendation for protection in the U.S. Although overvoltage protection requirements vary geographically, the basic concepts in T1.605 apply internationally.

Recommendation I.430 also specifies the behavior of the TE device in the presence of jitter and noise, which are not addressed in this document.

#### 3 Transformer Model

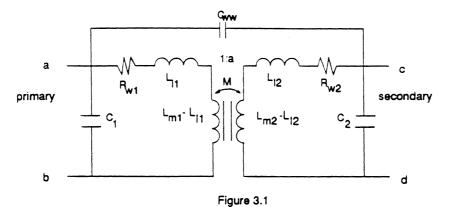

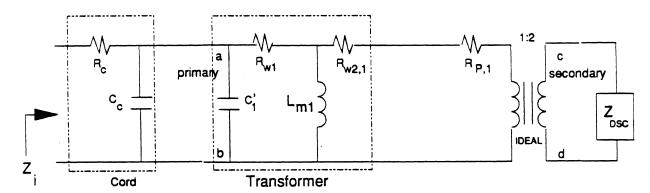

The transformer schematic depicted in Figure 3.1 represents the physical makeup of the transformer. It includes terms for leakage inductance, winding resistance, magnetizing inductance, and distributed capacitances. The placement of the coupled coils in this model makes analysis difficult.

In application with the DSC, the primary is connected to the S reference point and the secondary is connected to the pins of the DSC through a resistance. The turns ratio a must be 2.0.

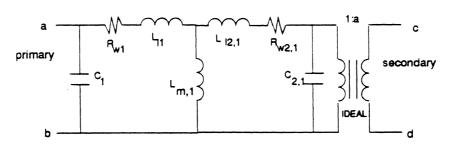

In Figure 3.2, the model is replaced with an equivalent model which incorporates an ideal transformer (infinite magnetizing inductance and no leakage) appended to a network of the actual transformer impedances. The ideal transformer allows loads connected to the secondary to be reflected into the primary precisely.

In this document, subscripts which include a comma followed by either a 1 or a 2 represent loads reflected into either the primary or the secondary. For example,  $R_{w2,1}$  is the secondary DC winding resistance referred to the primary.

Transformer Physical/Electrical Model

Figure 3.2

Primary Side Equivalent Model

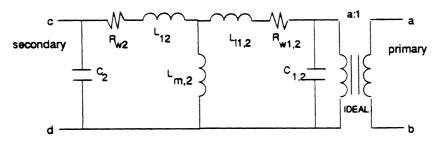

Figure 3.3 Secondary Side Equivalent Model

$$M = k\sqrt{L_{m_1} \times L_{m_2}}$$

$$L_{m,1} = \frac{M}{a}$$

$$L_{l_1} = L_{m_1} - \frac{M}{a}$$

$$L_{l_{2,1}} = \frac{L_{m_2}}{a^2} - \frac{M}{a}$$

$$L_{l_{1,1}} = L_{l_1} + L_{l_{2,1}}$$

$$R_{w_{2,1}} = \frac{R_{w_2}}{a^2}$$

$$C_{2,1} = a^2C_2$$

Several assumptions have been made:

- 1) The interwinding capacitance,  $C_{ww}$ , shown in Figure 3.1 is incorporated in the capacitors  $C_1$  and  $C_2$  of Figure 3.2. The further assumption is made that the cumulative affects of distributed capacitances, leakage inductances and resistances can be approximated by lumped impedances.

- 2) The value of k, the coefficient of coupling, is very close to unity. It can be shown that assuming that k=1 for the calculation of M results in no significant change to circuit performance. The values of  $L_{11}$  and  $L_{12}$  are then theoretically zero. The actual leakage inductance resulting from k slightly less than one is measureable in the lab. The measured value is the sum of  $L_{11}$  and  $L_{12,1}$ . It is not possible to isolate the value of either leakage inductance; however, only the sum of the two values is significant to circuit performance.

Figure 3.3 is the secondary side model, and the same assumptions apply. Reflection of impedances into the secondary yields:

$$L_{m,2} = a^{2} \cdot L_{m,1}$$

$$L_{l2} = a^{2} \cdot L_{l,1}$$

$$R_{w1,2} = R_{w1}a^{2}$$

$$C_{1,2} = \frac{C_{1}}{a^{2}}$$

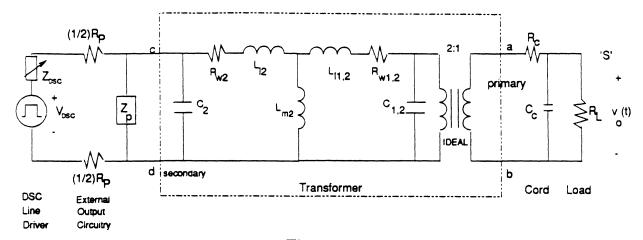

Figure 3.4 is a model of the important parameters influencing the output waveforms and input impedance of the TE.  $Z_{\rm DSC}$ , the device output impedance, varies depending on whether the DSC output is a mark or a space.  $Z_{\rm P}$  represents the protection network.

Figure 3.4

DSC Line Driver External Circuitry Model

## 4 Parameter and Template Measurement

The various lumped transformer parameters can be measured in the lab. Care must be taken so that the magnetic field is not saturated, resulting in erroneous measurement. For best results in terms of CCITT I.430 impedance testing, the test waveforms used should be at least 100 mV rms on the primary. For most accurate prediction of pulse shape, measurements should be made at the appropriate voltage levels, e.g. 750 mVp input at 96 kHz on the primary (line side) of the TE receiver and 2.326 Vp at 96 kHz at the secondary (circuit side) of the TE transmitter.

The magnetizing inductance  $L_{m,1}$  is measured at low frequency (2 to 20 kHz) across terminals ab with terminals cd open.

$L_{m,2}$  is measured at low frequency across terminals cd with ab open.

Leakage inductance  $L_{1,1}$  is measured across terminals ab at mid frequency (20 kHz to 1 MHz) with terminals cd shorted.

Leakage inductance  $L_{1,2}$  is measured across terminals cd at mid frequency (20 kHz to 1 MHz) with terminals ab shorted.

The transformer distributed capacitances are lumped into  $C_{ww}$ ,  $C_1$  and  $C_2$ . Measurement techniques vary, but no lump sum measurement can accurately model the distributed nature of these capacitances. The intended goal of the following technique is to measure the effect of the distributed capacitance and calculate a roughly equivalent lump sum value.

$C_1$  and  $C_2$  are calculated by determining the resonant frequency of the circuit made up of either capacitance and the leakage inductance. The resonant frequency

across terminals ab achieved when terminals cd are shorted is noted as  $f_1$ . At  $f_1$  the primary input impedance is greatest.  $C_1$  is then approximated as:

$$C_1 = \frac{1}{(L_{l,1}) (2\pi f_1)^2}$$

Likewise, shorting terminals ab and finding the resonant frequency looking into cd yields  $C_2$ :

$$C_2 = \frac{1}{(L_{l,2}) (2\pi f_2)^2}$$

In the following discussions, the effect of the interwinding capacitance  $C_{ww}$  is incorporated into  $C_1$  and  $C_2$ , and therefore  $C_{ww}$  does not appear directly in equations describing waveforms. The value is useful for determining energy transfer from primary to secondary during power surges and can be measured at high frequency (80 kHz to 1 MHz) across terminals ad with ab shorted and cd shorted.

DC resistance  $R_{w1}$  is measured across ab at DC with cd open.  $R_{w2}$  is measured across cd with ab open.

The receiver and transmitter must meet an impedance template, detailed in Section 3. Figure 4.1 describes the test conditions. The measurement on the transmitter is made while the transmitter is in idle mode, sending all pseudo-ternary spaces (1's). The measurement on the receiver can be done during any activation state.

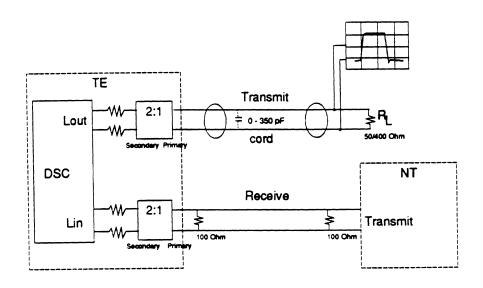

The pulse shape templates are applicable to the transmitter only. The test configuration is outlined in Figure 4.2. The TE is synchronized to the NT by means of connection to the receive pair from the S interface; however, the TE transmit pair is diverted from the S interface to a test load, including a TE connection cord. A test pattern is sent from the NT and looped back through the TE on a B channel, allowing any number of mark-space combinations.

Figure 4.1

Impedance Test Configuration

Figure 4.2

Pulse Shape Template Test Configuration

## 5 Impedance Template

TE's must conform to three impedance requirements, the first of which is the impedance template shown in Figure 2.2. The template allows roll-off at high and low frequencies, anticipating the impedance characteristics of the transformer. The template applies to the receiver at all times and to the transmitter when transmitting a pseudo-ternary space or when deactivated.

An applicable model of the interface components is shown in Figure 5.1, in which

component values have been reflected to the primary side of the transformer.

$C_c$  is the connecting cord capacitance, 350 pF maximum.  $C_1$  is the effective capacitance of the lumped components measured at the TE connector, and includes the reflected capacitance of any secondary side protection network or stray capacitances.  $L_{m,1}$  is the magetizing inductance of the transformer measured at the primary with an open circuit secondary.

At low frequency, the impedance is dominated by  $L_{m,1}$ :  $Z_i \approx j\omega L_{m,1}$

To meet the 250 Ohm recommendations at 2 kHz,  $L_{m,1}$  must be at least 20 mH for frequencies above 2 kHz.

Measuring at high frequency, the impedance is primarily capacitive:

$$Z_i \approx \frac{1}{j\omega(C_c + C_1')}$$

Matching the 1 MHz requirement of 200 Ohms, the maximum value of  $C_c+C_1$  is 800 pF, and therefore  $C_1$  must be less than 450 pF, measured below 1 MHz. Since secondary side capacitances are reflected into  $C_1$  by a factor of four, they must be less than 112.5 pF.

The second I.430 requirement limits energy absorbed at the fundamental line frequency of 96 kHz to 0.6 mA(peak) at 1.2 V(peak). That is, the impedance at 96 kHz, 1.2 V (peak) must equal or exceed 2000 Ohms.

The third requirement is a minimum output impedance of 20 Ohms during transmission of a mark. In this case,  $Z_{DSC}$  is very low, making the current limiting resistors significant. Guaranteeing that  $R_p/4 + R_{w1} + R_{w2,1}$  exceeds 20 Ohms satisfies the criterion.

Figure 5.1

Circuit Model for Impedance Measurement

## 6 50 Ohm Pulse Shape Template

The purpose of the following discussion is to present the dominant factors influencing the waveform of the output pulse. The actual arrangement of distributed transformer capacitance, resistance, and inductance, measurable only as lump sums, may greatly affect the waveform.

#### 6.1 Leading Edge Response

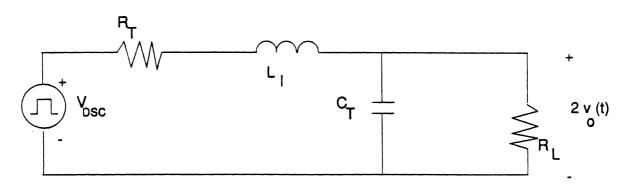

Figure 6.1 models significant circuit elements during the mark-to-space transition. The forcing function  $V_{\rm DSC}$  represents the DSC output drive and  $v_{\rm o}$  is the output voltage which appears on the S/T interface. The circuit is a simplified version of Figure 3.4, where:

$$R_T = R_P + R_{w2} + R_{w1,2}$$

$R_P \approx 78\Omega$  (external current limiting resistance)

$L_l = L_{l2} + L_{l1,2}$

$C_T = C_{1,2} + C_{c,2}$   $C_{c,2} \le 87.5 \text{pF}$   $C_{1,2} \le 112.5 \text{pF}$

$R_L = a^2 50\Omega = 200\Omega$

$V_{DSC} = \frac{V_s \omega_s}{s(s + \omega_s)}$

$V_s = \pm 2.326V$

$\omega_s \approx 31.4 \text{Mrad/sec}$

The connection cord resistance is neglected. C<sub>T</sub> represents capacitances which fall on the right (primary) side of the leakage inductance, including the cord and some transformer distributed capacitances.

Figure 6.1 Circuit Model at Space-to-Mark Transition

Nodal analysis yields the s-domain response for  $v_o$ :

$$V_o(s) = \frac{V_s \omega_s}{2L_t C_T} \cdot \frac{1}{s} \cdot \frac{1}{s + \omega_s} \cdot \frac{1}{s^2 + s\left(\frac{R_T}{L_t} + \frac{1}{R_L C_T}\right) + \frac{R_T R_L}{R_L} \cdot \frac{1}{L_t C_T}}$$

(Equation 6.1-1)

A damping coefficient for the quadratic denominator may be defined:

$$\zeta = \frac{\frac{R_T}{L_I} + \frac{1}{R_L C_T}}{2\sqrt{\frac{R_T + R_L}{R_L} \cdot \frac{1}{L_I C_T}}}$$

(Equation 6.1-2)

For typical component values,  $\zeta$  is greater than unity and the overdamped response can be rewritten:

$$V_o(s) = \frac{V_s \omega_s}{2L_1 C_T} \cdot \frac{1}{s} \cdot \frac{1}{s + \omega_s} \cdot \frac{1}{s \omega_1} \cdot \frac{1}{s + \omega_2}$$

(Equation 6.1-3)

Performing the inverse La Place transform:

$$v_0(t) = \frac{V_s \omega_s}{2L_t C_T} \left( a + b e^{-\omega_1 t} + c e^{-\omega_1 t} + d e^{-\omega_2 t} \right)$$

(Equation 6.1-4)

where the variables a,b,c,d and  $\omega_1, \omega_2$  depend on the values of the simplified model parameters.

## 6.2 Pulse Amplitude

The pulse amplitude is determined by evaluating the steady state value of  $v_o(t)$  in Equation 6.1-4. Since the variable a can be calculated as:

$$a = \frac{R_L L_l C_T}{(R_L + R_T) \omega_s}$$

$$\lim_{t \to \infty} v_o(t) = \frac{V_s}{2} \cdot \frac{R_L}{R_L + R_T}$$

(Equation 6.2-1)

Therefore, in order for the pulse amplitude to be  $\pm 750$  mV with  $V_s = \pm 2.326$  V,  $R_T$  must be 110 Ohms.

# 6.3 Trailing Edge Response

Figure 6.3 depicts a transmitter going from driving a mark to a space (undriven).  $C_2$  represents capacitances which can be attributed to the secondary side of the transformer, including surge protection network capacitances and

some transformer distributed capacitances.

As the driver output impedance changes from a very low value to a high value,  $C_2$  becomes the primary return path for the energy stored in the various reactive components at the beginning of the mark-to-space transition. As the reactive components discharge, energy circulates through the serial circuit formed by  $C_2$ ,  $L_1$ , and  $R_L$ . This serial RLC combination is typically underdamped, resulting in a ringing response which may not conform to the pulse template.

To combat the natural ringing response, the Am79C30A transmitter briefly shunts the C<sub>2</sub> capacitance before going to the high impedance state, dissipating

part of the energy through an overdamped resistive path.

Figure 6.3

Circuit Model For Mark-to-Space Transition with 50 Ohm Load

## 7 400 Ohm Pulse Shape Template

## 7.1 Leading Edge Response

Figure 6.1 and Equation 6.1-1 are still applicable. The increase of  $R_L$  to 1600 Ohms (400 Ohms reflected to the secondary) decreases the value of  $\zeta$  and typically forces  $V_o(s)$  to be underdamped:

$$V_o(s) = \frac{V_s \omega_s}{2L_t C_T} \cdot \frac{1}{s} \cdot \frac{1}{s + \omega_s} \cdot \frac{1}{(s + \alpha)^2 + \omega_0^2}$$

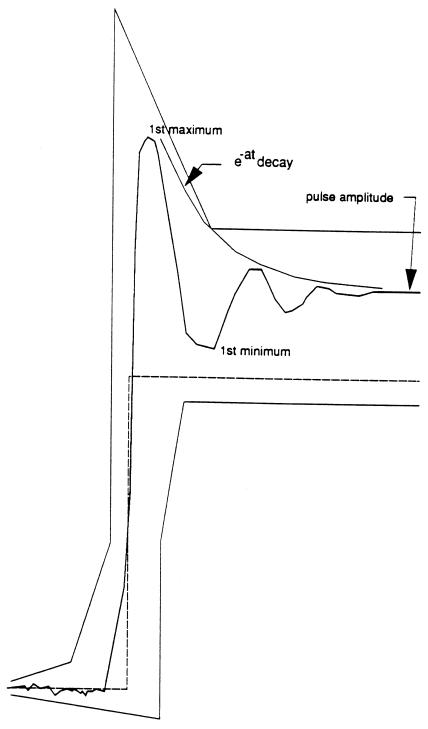

The time-domain representation of this response is  $v_o(t)$ , as shown in Figure 7.1

$$v_o(t) = \frac{V_s \omega_s}{2L_t C_T} \left( a + b e^{-\omega_s t} + c e^{-\alpha t} \cos(\omega_0 t) + d e^{-\alpha t} \sin(\omega_0 t) \right)$$

(Equation 7.1-1)

Figure 7.1 Leading Edge Response, 400 Ohm Test Load

## 7.2 Pulse Amplitude

The amplitude of the pulse is given by Equation 6.2-1. Assuming that  $R_{\tau}$  is 110 Ohms, as suggested in Section 6.2, the pulse amplitude is then 1.09 V, or 145% of the 750 mV nominal pulse amplitude.

## 7.3 Trailing Edge Response

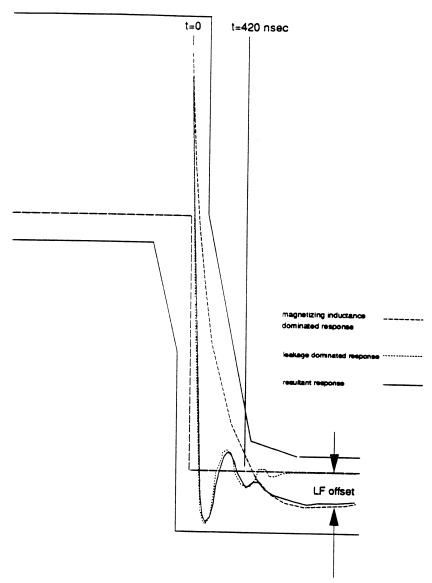

The circuit of Figure 6.3 applies to the 400 Ohm ( $R_L$  = 1600) load mark-to-space transition. In order to simplify expressions for the trailing edge response, the reaction is broken up into two components, an underdamped response dominated by the leakage inductance and an overdamped response dominated by the magnetizing inductance, both shown in Figure 7.3.0.

Figure 7.3.0 Mark-to-Space Transition, 400 Ohm Test Load

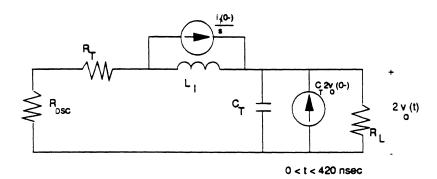

#### 7.3.1 Leakage Inductance Component

The initial 420 nsec of the trailing edge is dominated by the resonant circuit shown in Figure 7.3.1. The initial conditions  $i_t(0)$  and  $v_o(0)$  are determined by evaluating  $v_o(t)$  of Equation 6.1-4 at t=5.21 µsec ( $\lim_{t\to \infty}v_o(t)$  is a close approximation):

$$v_{o}(0) = \frac{V_{s}}{2} \frac{R_{L}}{R_{L} + R_{T}} \qquad i_{1}(0) = \frac{V_{s}}{R_{L} + R_{T}}$$

$$V_{o}(s) = v_{o}(0) \cdot \frac{s + \frac{R_{o}}{R_{L}} + \frac{i_{1}(0)}{C_{T} 2 v_{o}(0)}}{s^{2} + s \left(\frac{R_{o}}{L_{I}} + \frac{1}{R_{L} C_{T}}\right) + \frac{R_{o} R_{L}}{R_{L}} \cdot \frac{1}{L_{I} C_{T}}}$$

where:

$R_0 = R_T + R_{DSC}$

and  $R_{DSC} \cong 400\Omega$

$R_{\text{DSC}}$  is applied only during the initial 420 nsec in order to reduce ringing under the 50 Ohm load conditions.

The response is typically underdamped, resulting in the ringing shown in Figure 7.3.0.

Figure 7.3.1

Circuit Model for Leakage Dominated

Response, 400 Ohm Load, Mark-Space Transition

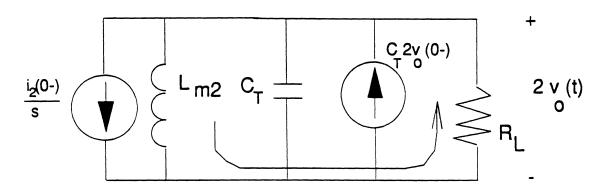

## 7.3.2 Magnetizing Inductance Component

The magnetizing inductance is much larger than the leakage and results in a slower response. During a mark (pseudo-ternary zero) energy is stored in the magnetic field of the transformer. During the transition from mark to space, the magnetizing inductance  $L_m$  continues to drive current in the same direction with a slow rate of decay, thereby adding to the pseudo-ternary

space a slowly decaying offset of polarity opposite that of the preceding mark. as demonstrated by the reverse loop current through R<sub>L</sub> in Figure 7.3.2.  $v_o(t)$  is an overdamped function described by:

$$V_o(s) = v_o(0^{-}) \frac{s - \frac{i_2(0^{-})}{2v_o(0^{-})C}}{s^2 + s\left(\frac{R_0 + R_L}{R_0 R_L C}\right) + \frac{1}{LC}}$$

where:

$C = C_{1,2} + C_2 + C_{c,2}$ and  $C_{1,2}$  and  $C_2$  represent the lumped effect of transformer and protection network capacitances.

$$i_2(0^-) = \frac{1}{L} \int_0^T v \, dt \approx \frac{2v_o(0^-)T}{L}$$

In the time domain:

$$v_o(t) = v_o(0) \left( a e^{-\omega_1 t} + b e^{-\omega_2 t} \right)$$

A typical curve is plotted in Figure 7.3.0.

The size of the initial offset is determined primarily by the initial current in  $L_m$ . Increasing the value of  $L_m$  reduces the offset by decreasing the amount of energy stored in the transformer core during the mark. Reducing  $L_m$  reduces the offset decay time.

**Figure 7.3.2** Circuit Model For Magnetizing Inductance Dominated Response, 400 Ohm Load

## 8 5.6 Ohm Pulse Requirements

CCITT Recommendation I.430 specifies that when a TE transmitter is driving a load of 5.6 Ohms, the output pulse amplitude does not exceed 20% of the nominal amplitude, i.e. 150 mV. The 5.6 Ohm load emulates the condition of a second TE driving a pulse of the opposite polarity on the S-interface.

Using Equation 6.2-1, the calculated amplitude of the pulse would be 197 mV, with  $R_L = 5.6 \times 4 = 22.4$  Ohms. In order to meet the 150 mV criterion, the DSC limits output current such that the actual pulse amplitude is approximately 115 mV.

#### 9 Conclusion

To maintain ISDN compatibility the passive component network in the interface of the DSC and the S/T reference point must be designed to meet the recommendations of CCITT I.430. Input and output impedances depend heavily on the transformer characteristics. Although detailed predictions of pulse shapes cannot be made easily due to the distributed nature of transformer parameters, the pulse shapes are controlled by identifiable subsets of those parameters and are predictable to a first order.

## 10 Transformer Recommendations

Table 10-1 describes a toroidal transformer used with the Am79C30A DSC as shown in Figure 1.1, where the capacitance of the protection network is limited to 65 pF and any standard ISDN basic access TE cord is used.

Table 10-1.

Transformer Recommendation

| Parameter        | Description                                                                             | Test Conditions                                                                       | Min      | Max  | Unit     |

|------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------|------|----------|

| а                | Turns ratio                                                                             | a:1 = secondary:primary                                                               | 1.96     | 2.04 |          |

| $L_{m1}$         | primary<br>inductance                                                                   | measured across a-b with<br>c-d open at 5 kHz,100 mV                                  | 22       |      | mH       |

| L <sub>1,2</sub> | leakage<br>inductance                                                                   | measured across c-d with a-b shorted at 1 MHz,                                        |          | 11   | μН       |

| $C_{d,1}$        | distributed capacitance                                                                 | 100 mV<br>measured across a-b with<br>c-d open at 1 MHz,100 mV                        |          | 180  | pF       |

| C <sub>ww</sub>  | interwinding capacitance                                                                | measured across a-c with<br>a-b and c-d shorted                                       |          | 130  | pF       |

| $R_{w1}$         | dc winding resistance                                                                   | at 1 MHz, 100 mV<br>measured across a-b<br>at 0Hz                                     |          | 3.0  | Ω        |

| $R_{w2}$         | dc winding resistance                                                                   | measured across c-d<br>at 0 Hz                                                        |          | 5.0  | Ω        |

| $\Delta I_{DC}$  | Tolerance to dc current imbalance                                                       | difference of currents I <sub>a.e</sub> and I <sub>b.e</sub> under DC bias conditions | 2.5      |      | mA       |

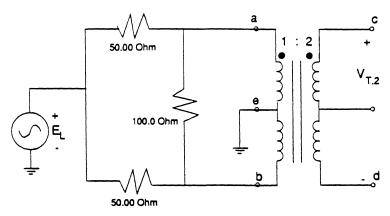

| LCL              | longitudinal conversion loss= $20 \log \left  \frac{\varepsilon_L}{v_{\tau,2}} \right $ | See Figure 10.1.<br>10 kHz < f < 300 kHz<br>f = 1 MHz                                 | 48<br>38 |      | dB<br>dB |

Figure 10.1. Longitudinal Balance Measurement

Table 10-2 lists transformers which were tested with the DSC. AMD has tested for conformance to CCITT I.430 impedance template, pulse shape templates, and longitudinal balance samples which the manufacturer states to be representative of all components of the same manufacturer part number. Although samples are confirmed to meet or exceed the requirements of I.430, no guarantees are implied.

Table 10-2 Transformer Part Numbers

| Manufacturer      | Part Number                        |  |  |

|-------------------|------------------------------------|--|--|

| BH Electronics    | 500-1720 (single transformer part) |  |  |

| BH Electronics    | 500-1717 (dual transformer part)   |  |  |

| Pulse Engineering | PE-64999 (single transformer part) |  |  |

| Pulse Engineering | PE-65499 (dual transformer part)   |  |  |

| Vacuumschmelze    | ZKB 402/521-52-261                 |  |  |